## ARTISAN° TECHNOLOGY GROUP

## Your **definitive** source for quality pre-owned equipment.

Artisan Technology Group

(217) 352-9330 | sales@artisantg.com | artisantg.com

#### Full-service, independent repair center

with experienced engineers and technicians on staff.

We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins.

#### **Custom engineering**

so your equipment works exactly as you specify.

Critical and expedited services

In stock / Ready-to-ship

- Leasing / Rentals / Demos

- ITAR-certified secure asset solutions

### Expert team | Trust guarantee | 100% satisfaction

All trademarks, brand names, and brands appearing herein are the property of their respective owners.

Find the Abaco Systems / SBS CTM19 at our website: Click HERE

GE Intelligent Platforms

# Hardware Reference Manual CM6 Single/Dual Core PowerPC® 3U CompactPCI® SBC Fourth Edition Publication No. HRMCM64E

imagination at work

Copyright © 2010 GE Intelligent Platforms, Inc. All rights reserved.

CM6 Hardware Reference Manual

This manual applies to the CM6 single or dual core MPC8641 3U CompactPCI® Single Board Computer hardware revision 1.0 and above until superseded by a higher revision.

## **Document History**

| Edition | Date       | Ву  | Chapter      | Comments                                                   |

|---------|------------|-----|--------------|------------------------------------------------------------|

| First   | 2007-10-29 | EH  | All          | Initial                                                    |

|         |            | HHS | Chapter 7    | Correct storage temperature values & styles (non-RoHS)     |

|         |            | HHS | All          | Cosmetic changes                                           |

|         |            | HHS | All          | Continued after crash                                      |

|         |            | EH  | All          | Adapted for hardware revision 1.x                          |

|         |            | EH  | All          | Implement correctives                                      |

|         |            | MF  | All          | Prepared for preliminary release                           |

|         |            | EH  | Env. cond.   | add temp chart                                             |

|         |            |     | Elect. char. | RS244/RS485                                                |

|         |            | HHS | All          | Adjust page breaks                                         |

|         |            |     | Page 2       | Insert new document history table                          |

|         |            | HHS | All          | Update TOC etc.                                            |

|         |            | HHS | All          | Cleanup minor errors; cosmetic changes                     |

| Second  | 2008-12-15 | EH  | Chapter 7    | add power and thermal characteristics of CPU types         |

|         |            |     | Chapter 6    | add memory speed restrictions                              |

|         |            | HHS | All          | Change SBS to GE Intelligent Systems                       |

|         |            |     |              | spell-checking                                             |

|         |            | EH  | Chapter 6    | add description of the serial auto load EEPROM             |

|         |            |     | PMC Site     | programming                                                |

|         |            |     | Compact      |                                                            |

|         |            |     | PCI          |                                                            |

|         |            | HHS | All          | Change copyright to 2008; change hidden SBS references     |

|         |            | EH  | Real Time    | limit the STORE operations to 200k cycles                  |

|         |            |     | Clock        |                                                            |

|         |            | HHS | All          | Cosmetic changes; change Embedded Systems to               |

|         |            |     |              | Intelligent Platforms in footers                           |

|         |            | EH  | Env. cond.   | add card edge temp for 8-style                             |

|         |            | HHS | All          | Correct company name; web site address                     |

|         |            | HHS | All          | Cosmetic changes; correct email addresses; remove          |

|         |            |     |              | Chinese address                                            |

|         |            | HHS | Ch. 2 & 6    | Insert note on NON-transparent operation                   |

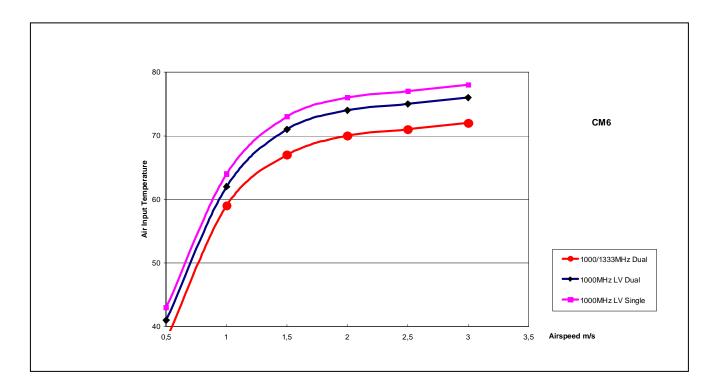

| Third   | 2009-03-09 | EH  | Ch 7         | Add curve for single core 1000 MHz low voltage in heat     |

|         |            |     |              | sink diagram                                               |

|         |            | EH  | Ch 7         | Add curve for single core 1000 MHz low voltage in heat     |

|         |            |     |              | sink diagram                                               |

| Fourth  | 2010-03-30 | EH  | all          | Remove PMC PCI-X capability                                |

|         |            | HHS | Ch 4         | Add info & figure about secondary thermal interface        |

|         |            |     | all          | correct footer text; adapt for chapter start on odd pages; |

|         |            |     |              | change © dates to 2009                                     |

|         |            | EH  | Table 9      | Register RSR Bit 4 must be cleared before a new CPU        |

|         |            |     |              | request can be performed                                   |

|  | HHS | Title | Change title & footer to 'Hardware Reference' Manual |

|--|-----|-------|------------------------------------------------------|

|  | EH  |       | Table 7 and Table 8 pin PMCIO31 added                |

|  | EH  |       | Pinout J7002 corrected (PMCIO06/07)                  |

|  | HHS | All   | Change front and rear pages; correct support section |

|  | HHS | All   | Correct support chapter; add sales addresses         |

### Legal Information

#### Legal Disclaimers

© 2010 GE Intelligent Platforms, Inc. All rights reserved.

The information in this manual is proprietary to and is the confidential information of GE Intelligent Platforms, Inc. and may not be reproduced in whole or in part, for any purpose, in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent of GE Intelligent Platforms, Inc. Use, disclosure, and reproduction is permitted only under the terms of a GE Intelligent Platforms license agreement or explicit written permission of GE Intelligent Platforms. You are not authorized to use this document or its contents until you have read and agreed to the applicable license agreement. Receipt of this publication is considered acceptance of these conditions.

All information contained in this document has been carefully checked and is believed to be entirely reliable and consistent with the product that it describes. However, no responsibility is assumed for inaccuracies. GE Intelligent Platforms assumes no liability due to the application or use of any product or circuit described herein; no liability is accepted concerning the use of GE Intelligent Platforms products in life support systems. GE Intelligent Platforms reserves the right to make changes to any product and product documentation in an effort to improve performance, reliability, or design.

THIS DOCUMENT AND ITS CONTENTS ARE PROVIDED AS IS, WITH NO WARRANTIES OF ANY KIND, WHETHER EXPRESS OR IMPLIED, INCLUDING WARRANTIES OF DESIGN, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM ANY COURSE OF DEALING, USAGE, OR TRADE PRACTICE.

Changes or modifications to this unit, not expressly approved by GE Intelligent Platforms, could void the user's authority to operate the equipment.

All computer code and software contained in this document is licensed to be used only in connection with a GE Intelligent Platforms hardware product. Even if this code or software is merged with any other code or software program, it remains subject to the terms and conditions of this license. If you copy, or merge, this code or software, you must reproduce and include all GE Intelligent Platforms copyright notices and any other proprietary rights notices.

The content of this manual if furnished for informational use only and is subject to change without notice. Reverse engineering of any GE Intelligent Platforms product is strictly prohibited.

In no event will GE Intelligent Platforms be liable for any lost revenue or profits or other special, indirect, incidental and consequential damage, even if GE Intelligent Platforms has been advised of the possibility of such damages, as a result of the usage of this document and the software that this document describes. The entire liability of GE Intelligent Platforms shall be limited to the amount paid by you for this document and its contents. GE Intelligent Platforms shall have no liability with respect to the infringement of copyrights, trade secrets, or any patents by this document of any part thereof. Please see the applicable software license agreement for full disclaimer or warranties and limitations of liability.

This disclaimer of warranty extends to GE Intelligent Platforms' licensees, to licensees transfers, and to licensees customers or users and is in lieu of all warranties expressed, implied, or statutory, included implied warranties of scalability or fitness for a particular purpose.

GE Intelligent Platforms and the GE Intelligent Platforms logo are trademarks of GE Intelligent Platforms, Inc. Other brand names and product names contained herein may be claimed as the property of others.

GE Intelligent Platforms, Inc., 2500 Austin Drive, Charlottesville, VA 22911, U.S.A.

#### **Regulatory compliance**

Products sold or transferred between companies or operated on company premises (factory floor, laboratory) do not need CE, FCC or equivalent certification. Boards or subsystems which cannot provide a useful function on their own do not need certification.

Certification can only be granted to complete and operational systems. There are authorized testing agencies, regulatory organizations and laboratories who will issue certificates of compliance after system testing.

GE Intelligent Platforms designs and tests all their products for EMI/EMC conformance. Where GE Intelligent Platforms supplies a complete/functional system for use by end users a certificate will be cited in the manuals/documents which are provided with the products.

Products manufactured by GE Intelligent Platforms should normally be suitable for use in properly designed and produced customer equipment (system boxes or operational systems) without any major redesign or additional filtering. However, the systems might not conform to specific regulations once assembled and used. The system integrator or installer must test for compliance as required in his country or by the intended application and certify this to the end user.

#### **ESD/EMI** issues

ESD (Electro-Static Discharge) and EMI (Electro-Magnetic Interference) issues may show up in complete and operational systems. There are many ways to avoid problems with these issues.

Any operational system with cables for I/O signals, connectivity or peripheral devices provides an entry point for ESD and EMI. If GE Intelligent Platforms does not manufacture the complete system, including enclosure and cables, it is the responsibility of the system integrator and end user to protect their system

against potential problems. Filtering, optical isolation, ESD gaskets and other measures might be required at the physical point of entry (enclosure wall of box or rack). For example it is state-of-the-art that protection can not be done at the internal connector of an RTM if a cable is attached and routed outside the enclosure. It has to be done at the physical entry point as specified above.

Products manufactured by GE Intelligent Platforms should normally be suitable for use in properly designed and produced customer equipment (system boxes or operational systems) without any major redesign. However, the systems might be subject to problems and issues once assembled, cabled and used. The end user, system integrator or installer must test for possible problems and in some cases show compliance to local regulations as required in his country or by the intended application.

### **Corporate addresses**

#### **Corporate headquarters**

GE Intelligent Platforms, Inc. 2500 Austin Drive Charlottesville, VA 22911 U.S.A.

Phone: +1-800-322-3616 Web: www.ge-ip.com

#### **Regional headquarters**

| US                                                                    | Germany                                |  |

|-----------------------------------------------------------------------|----------------------------------------|--|

| Americas & Pacific Rim (Japan,<br>Korea, China, Philippines, AUS, NZ) | Germany                                |  |

| GE Intelligent Platforms, Inc.                                        | GE Intelligent Platforms GmbH & Co. KG |  |

| 2500 Austin Drive                                                     | Memminger Str. 14                      |  |

| Charlottesville, VA 22911                                             | 86159 Augsburg                         |  |

| U.S.A.                                                                | Germany                                |  |

| Phone: +1-800-322-3616                                                | Phone: +49-821-5034-0                  |  |

| Fax: +1-                                                              | Fax: +49-821-5034-119                  |  |

| Web: www.ge-ip.com                                                    | Email: sales.augsburg.ip@ge.com        |  |

GE Intelligent Platforms on the Web: http://www.ge-ip.com

For contact and other information (service, warranty, support etc.) see address list in chapter: 'Support, Service'.

## Welcome

The CM6 CompactPCI Single Board Computer is a PowerPC stand-alone CPU board equipped with numerous functions and add-on features on a minimum board size. This technical manual is designed to provide information regarding the general usage and application of the CM6 CompactPCI Single Board Computer. The hardware design is also outlined.

Chapter 1 gives an overview of the functions, features and devices of the CM6. Chapter 2 and 3 illustrate unpacking and installation procedures.

Chapter 4 describes all onboard and panel interfaces with pin assignments.

Chapter 5 contains notes on system resources.

Chapter 6 lists details of function blocks.

Chapter 7 outlines electrical, mechanical and environmental specifications.

Appendix A:

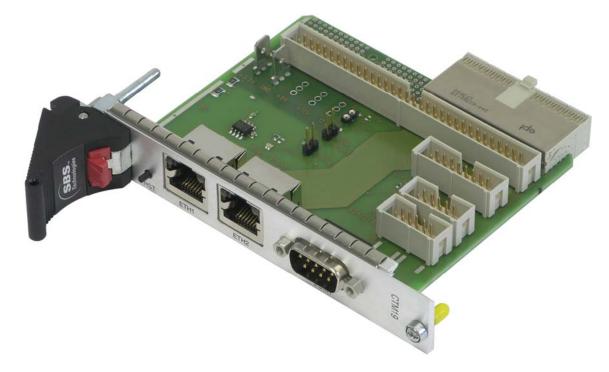

The CTM19 transition module is available for the CM6. This board will provide easy access to the rear CM6 interfaces.

Appendix B: Support, Service and Warranty Information.

Please observe all safety instructions when handling GE Intelligent Platforms products as given in the unpacking and installation chapters.

All documents will be included as files on the Technical Product Information CD-ROM.

#### **Typographic Conventions**

This manual uses the following notation conventions:

- *Italics* (sometimes additional in *blue* color) emphasize words in text or documentation or chapter titles or web addresses if underlined.

- Hexadecimal values (base 16) are represented as digits followed by "h", for example: 0Ch.

- Hexadecimal values (base 16) are represented as digits preceded by "H", for example: **H**0C.

- Hexadecimal values (base 16) are represented as digits preceded by "\$", for example: \$0C.

- Binary values (base 2) are represented as digits followed by "b", for example 01b

- The use of a "#" (hash) suffix to a signal name indicates an active low signal. The signal is either true when it is at logic zero level (voltage close to 0 V) or the signal initiates actions on a high-to-low transition.

- The use of a "\" (backslash) prefix to a signal name indicates an active low signal. The signal is either true when it is at logic zero level (voltage close to 0 V) or the signal initiates actions on a high-to-low transition.

- Text in Courier font indicates a command entry or output from a GE Intelligent Platforms embedded PC product using the built-in character set.

- Notes, warning symbols and cautions call attention to essential information.

#### **Product Properties**

#### Certification

The product or products described in this technical manual cannot be operated by themselves. They are components for integration into operational systems or add-ons to such systems. The products have been designed to meet relevant regulatory standards like FCC and CE. As mandated by these standards conformance to these standards can only be certified for complete operational systems. This has to be done by the end-user or by the systems integrator in their operational systems. GE Intelligent Platforms have tested some products in their own systems. Upon request information is available which products have been tested and about the specific environment under which GE Intelligent Platforms has tested these components.

#### Altitude

Altitude, air pressure and ambient temperature influence the thermal operation of the components described in this manual. They have been developed and tested at about 500 m (1650 ft.) above sea level at a typical ambient temperature of 20 °C (68 °F). Because of only marginal variations within a limited range of altitudes these products operate as specified within altitudes from sea level to 1000 m (3300 ft.). GE Intelligent Platforms can assist the user of these components in planning operation outside this altitude range upon request.

#### Options

This manual describes the basic product plus all options. Your product may not have all options implemented. Please verify with your purchase contract which options are implemented. Descriptions of options which are not implemented obviously do not apply to your product.

## Support, Service and Warranty

The manufacturer grants the original purchaser of GE Intelligent Platforms products a warranty of 24 months from the date of delivery. For details regarding this warranty refer to Terms & Conditions of the initial sale.

Please see chapter "Support, Service, and Warranty Information" on page 84 for further details on repairs and product support.

For support on the web and product information, visit our website at <u>http://www.ge-ip.com</u>

## Contents

|           | Legal Information             | 5  |

|-----------|-------------------------------|----|

|           | Legal Disclaimers             | 5  |

|           | Regulatory compliance         | 6  |

|           | ESD/EMI issues                | 6  |

|           | Corporate addresses           | 7  |

|           | WELCOME                       | 9  |

|           | Product Properties            | 10 |

|           | Support, Service and Warranty | 11 |

|           | CONTENTS                      | 13 |

| CHAPTER 1 | INTRODUCTION                  | 19 |

|           | Design Features               | 20 |

| CHAPTER 2 | UNPACKING AND INSPECTION      | 25 |

|           | ESD                           | 25 |

|           | Unpacking and Handling        | 26 |

|           | Initial Inspection            | 27 |

|           | Delivery Volume               | 27 |

|           | Available Accessories         | 28 |

|           |                               |    |

| CHAPTER 3 | INSTALLATION                                             | 29       |

|-----------|----------------------------------------------------------|----------|

|           | General advice                                           | 29       |

|           | Unpacking and Handling                                   | 29       |

|           | ESD<br>Concret Advisories                                | 29       |

|           | General Advisories<br>Advisories for CompactPCI products | 30<br>30 |

|           | Minimum System Requirements                              | 30       |

|           | Installation                                             | 30       |

|           | Initial Power-On Operation                               | 31       |

| CHAPTER 4 | INTERFACES                                               | 33       |

|           | Front Panel Interfaces                                   | 34       |

|           | CM6 Connectors                                           | 34       |

|           | CPCI connector reference                                 | 34       |

|           | PMC Connectors J7101, J7102, J7103 and J7104             | 37       |

|           | Secondary Thermal Interface                              | 37       |

| CHAPTER 5 | RESOURCES                                                | 45       |

|           | Address Map                                              | 45       |

|           | Local Bus Controller                                     | 45       |

|           | CPLD Registers                                           | 46       |

|           | Status Input Ports                                       | 51       |

|           | General Purpose I/O Port                                 | 51       |

|           | Interrupts                                               | 52       |

|           | PCI Busses                                               | 52       |

|           | SMBusses                                                 | 52       |

|           | SMBus 1                                                  | 52       |

|           | SMBus 2                                                  | 53       |

| CHAPTER 6 | FUNCTION BLOCKS                                          | 55       |

|           | Processor                                                | 55       |

GE Intelligent Platforms – CM6 Hardware Reference Manual, Fourth Edition

Page 14

| Clock Assignment           | 55 |

|----------------------------|----|

| Memory Controller          | 56 |

| Flash Memory               | 56 |

| Flash Write Protection     | 56 |

| PCI Express Bus            | 57 |

| PMC Site                   | 57 |

| Compact PCI                | 57 |

| Watchdog                   | 58 |

| nvSRAM Real Time Clock     | 58 |

| Serial Interface           | 59 |

| Ethernet Interface         | 59 |

| General Purpose I/O        | 60 |

| Interrupt Circuitry        | 60 |

| COP Debug Interface        | 60 |

| JTAG Interface             | 60 |

| Temperature                | 61 |

| SMBus devices              | 61 |

| Serial EEPROMs             | 61 |

| Digital Switch             | 62 |

| LED                        | 62 |

| Reset                      | 63 |

| SPECIFICATIONS             | 65 |

| Voltage Requirements       | 65 |

| Power Consumption          | 66 |

| Environment Conditions     | 67 |

| Electrical Characteristics | 69 |

| General Purpose IO 0-7     | 69 |

| COM1 RS232 Interface       | 69 |

|                            |    |

CHAPTER 7

|            | COM2 RS422/485 Interface<br>Isolation                  | 70<br>70 |

|------------|--------------------------------------------------------|----------|

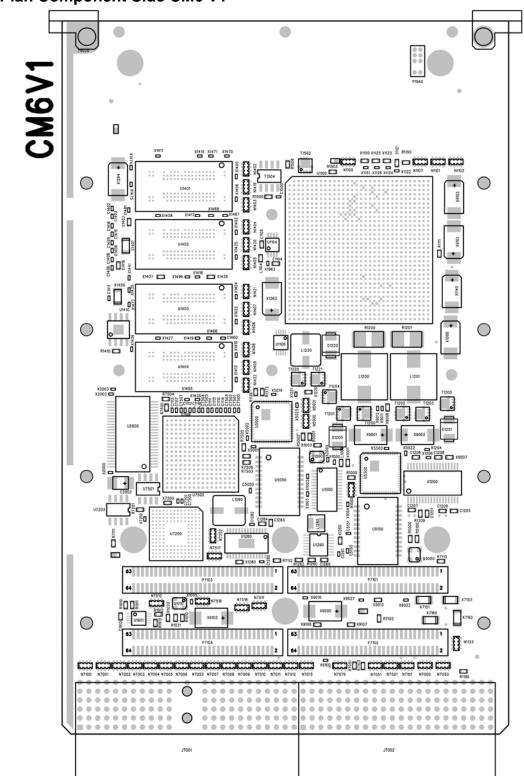

|            | Placement Plan Component Side CM6 V1                   | 71       |

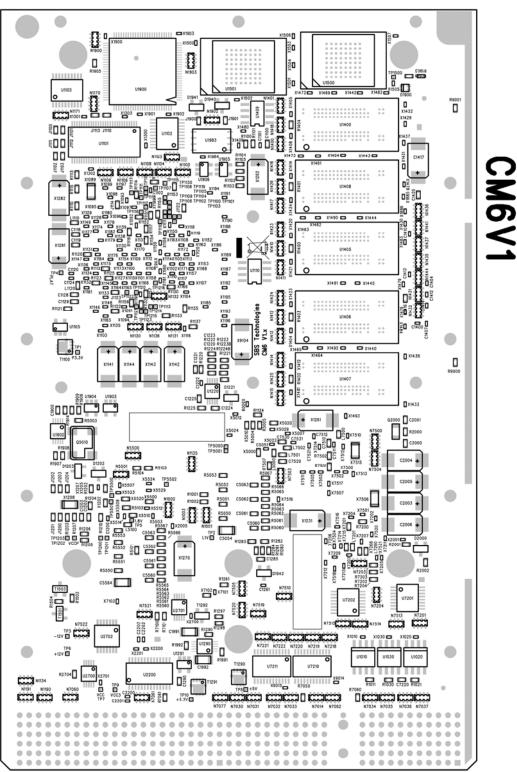

|            | Placement Plan Solder Side CM6 V1                      | 72       |

| APPENDIX A | TRANSITION MODULE CTM19                                | 73       |

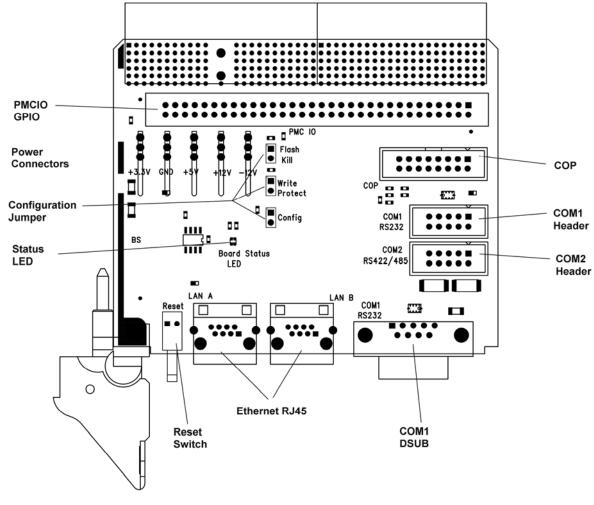

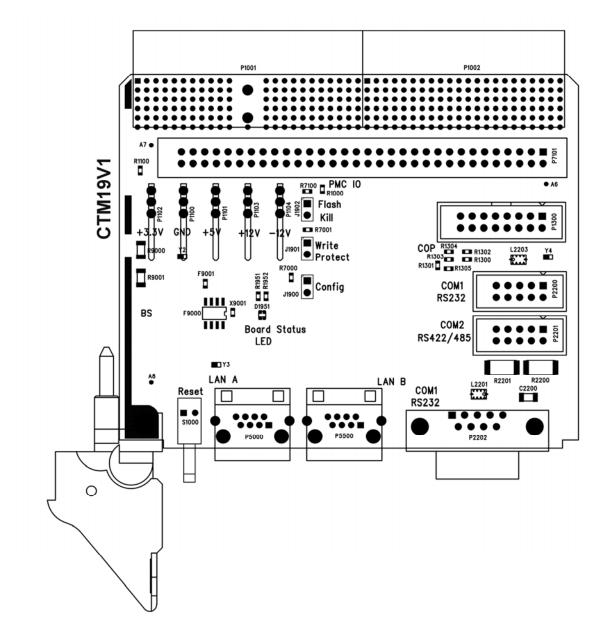

|            | CTM19 Interfaces                                       | 74       |

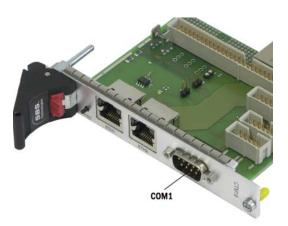

|            | Serial Interfaces COM1 (P2200, P2202) and COM2 (P2201) | 74       |

|            | COP Interface P1300                                    | 76       |

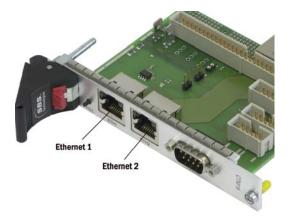

|            | Ethernet connectors P5000, P5500                       | 77       |

|            | Configuration jumpers J1900, J1901, J1902              | 78       |

|            | PMCIO connector P7101                                  | 78       |

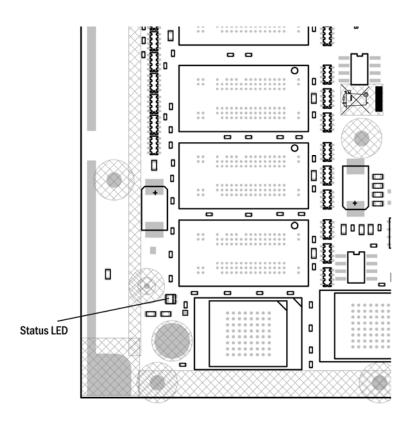

|            | Board Status LED                                       | 80       |

|            | Reset Button                                           | 80       |

|            | Power connectors P1100, P1101, P1102                   | 80       |

|            | cPCI connectors P1001, P1002                           | 80       |

|            | Placement Plan CTM19                                   | 82       |

| APPENDIX B | SUPPORT, SERVICE AND WARRANTY                          | 83       |

|            | Geographical Regions                                   | 83       |

|            | Technical Support                                      | 83       |

|            | Support on the Web                                     | 84       |

|            | Warranty                                               | 84       |

|            | Error Report                                           | 84       |

## LIST OF FIGURES

| FIGURE 1: CM6 BOARD VERSIONS                                            |    |

|-------------------------------------------------------------------------|----|

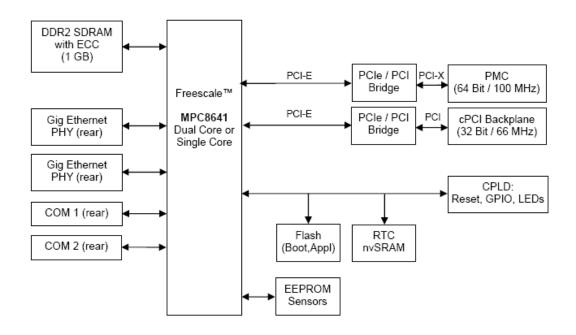

| FIGURE 2: BLOCK DIAGRAM OF CM6                                          |    |

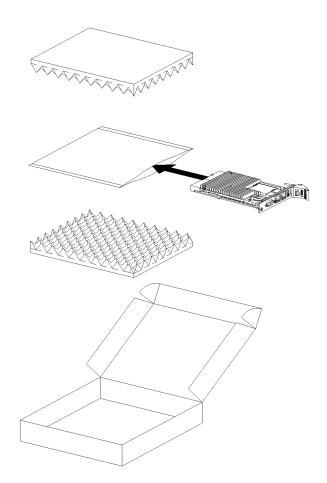

| FIGURE 3: PACKAGING MATERIAL                                            |    |

| FIGURE 4: BOARD HANDLING                                                |    |

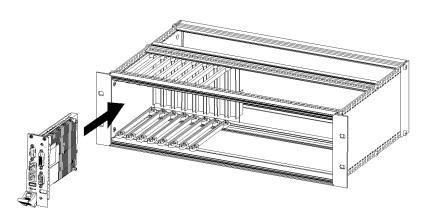

| FIGURE 5: BOARD IN CARD CAGE                                            |    |

| FIGURE 6: BOARD PHOTO                                                   |    |

| FIGURE 7: CM6 FRONT PANEL                                               |    |

| FIGURE 8: MOUNTING OF SECONDARY THERMAL INTERFACE ON PMC MODULE         |    |

| FIGURE 9: LED                                                           |    |

| FIGURE 10: HEAT SINK DIAGRAM FOR AIR COOLED VERSIONS (1-,2-,3-,4-STYLE) |    |

| FIGURE 11: PLACEMENT DIAGRAM COMPONENT SIDE                             | 71 |

| FIGURE 12: PLACEMENT DIAGRAM SOLDER SIDE                                |    |

| FIGURE 13: TRANSITION MODULE CTM19                                      |    |

| FIGURE 14: LAYOUT OF TRANSITION MODULE                                  | 74 |

| FIGURE 15: COM1 AT TRANSITION MODULE                                    |    |

| FIGURE 16: ETHERNET CONNECTORS                                          | 77 |

| FIGURE 17: RJ45 ETHERNET CONNECTORS                                     | 77 |

| FIGURE 18: PLACEMENT PLAN CTM19                                         |    |

|                                                                         |    |

## LIST OF TABLES

| TABLE 1: DELIVERY VOLUME                                                        | 27 |

|---------------------------------------------------------------------------------|----|

| TABLE 2: ACCESSORY OPTIONS FOR CM6                                              |    |

| TABLE 3: CM6 CONNECTORS                                                         |    |

| TABLE 4: CPCI CONNECTORS J7001 AND J7002                                        |    |

| TABLE 5: PMC CONNECTOR PIN ASSIGNMENTS.                                         |    |

| TABLE 6: P7104 CONNECTOR PIN ASSIGNMENTS                                        |    |

| TABLE 7: P7104/P7002 CONNECTORS PIN ASSIGNMENTS                                 |    |

| TABLE 8: P7104/P7002 CONNECTORS PIN ASSIGNMENTS                                 |    |

| TABLE 9: RESET SOURCE REGISTER (RSR)                                            |    |

| TABLE 10: CONTROL REGISTER (CR)                                                 |    |

| TABLE 11: STATUS REGISTER 0 (STAT0)                                             |    |

| TABLE 12: STATUS REGISTER 1 (STAT1)                                             |    |

| TABLE 13: WATCHDOG REGISTER (WCR)                                               |    |

| TABLE 14: WATCHDOG TRIGGER (WTIG)                                               |    |

| TABLE 15: BOOT CODE REGISTER (PCR)                                              |    |

| TABLE 16: PLD VERSION REGISTER (VER)                                            |    |

| TABLE 17: ETSEC1                                                                | 51 |

| TABLE 18: ETSEC2                                                                | 51 |

| TABLE 19: GPIO                                                                  |    |

| TABLE 20: INTERRUPTS                                                            |    |

| TABLE 21: SMBUS DEVICES                                                         |    |

| TABLE 22: REAR I/O LED INDICATION                                               |    |

| TABLE 23: BOOT AND STATUS LED INDICATION                                        |    |

| TABLE 24: RESET SOURCES                                                         |    |

| TABLE 25: VOLTAGE REQUIREMENTS                                                  |    |

| TABLE 26: POWER CONSUMPTION                                                     |    |

| TABLE 27: TEMPERATURE AND HUMIDITY CONDITIONS                                   |    |

| TABLE 28: SHOCK AND VIBRATION CONDITIONS                                        |    |

| TABLE 29: SHOCK AND VIBRATION CONDITIONS                                        |    |

| TABLE 30: MAXIMAL CARD EDGE TEMPERATURE FOR CONDUCTION COOLED VERSION (8-STYLE) |    |

| TABLE 31: GPIO INPUT SIGNAL VOLTAGES                                            |    |

| TABLE 32: GPIO OUTPUT VOLTAGE SIGNAL LEVELS                                     |    |

| TABLE 33: COM1 ELECTRICAL CHARACTERISTICS                                       |    |

| TABLE 34: COM2 ELECTRICAL CHARACTERISTICS                                       |    |

| TABLE 35: COM1 AT TRANSITION MODULE                                             |    |

| TABLE 36: COM2 AT TRANSITION MODULE                                             |    |

| TABLE 37: COP DEBUG INTERFACE (P1300)                                           | 76 |

| TABLE 38: ETHERNET PIN ASSIGNMENTS (P5000 & P5500)                              |    |

| TABLE 39: MISCELLANEOUS CONNECTOR P8100                                         |    |

| TABLE 40: BOARD FAIL LED AT CTM19                                               |    |

## CHAPTER 1 Introduction

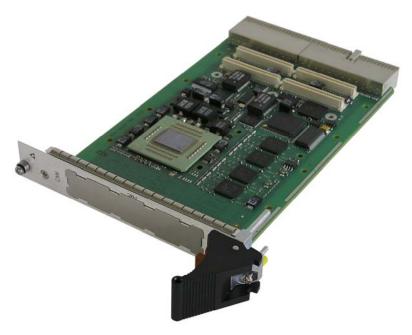

Figure 1: CM6 board versions

#### **Board Design**

The SBC (Single Board Computer) CM6 is a PowerPC with single/dual core CPU. It is equipped with many functions a conventional SBC can only offer with several add-on cards. The CM6 offers configurations for either convection cooled or conduction cooled environment. Extension boards can be connected via the CPCI interface and/or PMC interface. The minimized board size and the number of interfaces and functions allow the CM6 to be used in many applications. See the following block diagram for the board design.

Figure 2: Block diagram of CM6

## **Design Features**

The CM6 CompactPCI Single Board Computer features:

#### Microprocessor

Single or dual e600 core Freescale® PowerPC<sup>™</sup> MPC8641 On-chip 32 Kbytes instruction + 32 kBytes data first level cache On-chip 1Mbyte second level cache integrated Integrated system logic required for networking, storage and general purpose embedded applications. Freescale® single core PowerPC<sup>™</sup> MPC8641 processor 1000 MHz-1500 MHz Freescale® dual core PowerPC<sup>™</sup> MPC8641D processor 1000 MHz-1333 MHz

#### DRAM

DDR2 memory controller with one bank,

512 MByte, 1 GByte, 2 GByte (future) DDR2 SDRAM, memory interface with up to 333 MHz memory frequency and 667 MHz data rate (depending from used CPU and environment condition) Each memory bank is ECC controlled and on-board soldered

#### **NVRAM**

NVRAM build with a 1 Mbit Serial EEPROM via the SMBus

#### Flash

Up to 128 MByte (future 256 MByte) Flash which includes a Boot Program, Flash devices write protected by software or hardware jumper

#### System Controller

Integrated in MPC8641 Internal CPU MPX bus up to 333MHz DDR2 SDRAM Controller supports up to 4 Gbit devices Two PCI Express interfaces Local Bus interface to external devices Two integrated Gigabit Ethernet MAC controllers Two DUART 4-wire interfaces

#### NVSRAM/Real Time Clock

128kByte non-volatile SRAM and RTC device (max 200k STORE operations) RTC has no external power back-up and will loose time and date after power off

## Watchdog

Two stage Watchdog with interrupt and reset

#### Timer/Counter

8 timers each 32-bit wide for system timing and periodic interrupt

#### PMC slot

One 64-bit 66MHz PCI mezzanine slot for standard PMC as well as for rugged PMC. Part of PMC IO signals available at the rear connectors.

#### Ethernet

Two Gigabit Ethernet ports at rear

#### Serial IO

Two serial channels each has a 4-wire interface COM1 with RS232 driver COM2 with RS422/485 driver

#### **General Purpose IO**

8-bit general purpose IOs individually programmable for input, output and triggered interrupt IO signals are available at rear IO (alternative with PMC IO)

#### CPCI bus

Compact PCI Bus with PCIe/PCI Bridge Pericom PI7C9X110 PICMG 2.0 R3.0 complaint CPCI local bus standard, 32 bit interface for up to 7 slots at 33 MHz or 4 peripheral slots at 66 MHz Standard 3U backplanes can be used

Onboard Pull-up resistors are optimized for 3.3 V I/O voltage, but 5 V I/O can also be used for 33 MHz

#### System/non-System

The CM6 board can be used either as system or peripheral board at the cPCI bus

#### COP Interfaces Processor debug interface for external emulator at rear

#### JTAG Interface

JTAG interface for all devices with JTAG interface accessible at the cPCI connector

#### Flash Kill

Optional the user can destroy the Flash devices and its content for security reasons (contact factory)

#### **Strapping Configurations**

Strapping configurations are available from rear Hardware write-protection for all programmable devices Software configuration select Flash kill option

#### **Required Power Voltages**

+3.3 V, +5 V +12 V and -12 V for supply for PMC modules +12 V for Flash Kill option

Conduction Cooling Conduction Cooling available

#### **Conformal Coating**

The board can optionally be conformal coated to protect against humidity and fungus devices, configuration selection

#### LED Indicators

CPU Fail LEDs at rear. Status and user LED at board for debugging

Temperature Sensors Temperature sensor (LM86) show the temperature of the system board near CPU and CPU die temperature CPU voltage is shut-off when die temperature reaches 110 °C or board temperature reaches 95 °C

Front Panel Front panel with PMC opening

#### Backpanel IO

COM1-2, GPIO<sup>1)</sup>, Reset, PMC IO<sup>1)</sup>, 2x Gigabit Ethernet, Boot Select, HW Write Protect, Flash Kill<sup>1)</sup>, COP Transition module CTM19 available for compatible connectors<sup>1)</sup> depends on PMC IO configuration

### Approvals

Designed to meet UL (PCB has 94V-0, Self-extinguishing within 10 seconds, no flame drips which ignite)

## CHAPTER 2 Unpacking and Inspection

#### **Chapter Scope**

This chapter covers the suggested inspection and preparation considerations and background information necessary prior to using the CM6. Unpacking, initial inspection and first-time operation of the CM6 are covered. Following the procedures given in this chapter is recommended, since they will verify proper operation after shipping and before the product is integrated into your system.

### ESD

#### **Electrostatic Discharge Notice**

The discharge of static electricity, known as Electro Static Discharge or ESD, is a major cause of electronic component failure. The CM6 has been packed in a static-safe bag which protects the board from ESD while the board is in the bag. Before removing the CM6 or any other electronic product from its static-safe bag, be prepared to handle it in a static-safe environment.

You should wear a properly functioning anti static strap and ensure you are fully grounded. Any surface upon which you place the unprotected CM6 should be static-safe, usually facilitated by the use of anti static mats. From the time the board is removed from the anti static bag until it is in the card cage and functioning properly, extreme care should be taken to avoid 'zapping' the board with ESD. You should be aware that you could 'zap' the board without you knowing it; a small discharge, imperceptible to the eye and touch, can often be enough to damage electronic components. Extra caution should be taken in cold and dry weather when static easily builds up.

### **Unpacking and Handling**

Although the CM6 is carefully packaged against the rigors of shipping, it is still possible that shipping damages can occur. Careful inspection of the shipping carton should reveal some information about how the package was handled by the shipping service. If evidence of damage or rough handling is found, you should notify the shipping service and GE Intelligent Platforms as soon as possible.

**Figure 3: Packaging Material**

Retain all packing material in case of future need. Only after ensuring that both you and the surrounding area are protected from ESD, carefully remove the CM6 from the shipping carton by grasping it by the front panel and the connectors. Place the board, in its anti static bag, flat down on a suitable surface. You may then remove the board from the anti static bag by tearing the ESD warning labels.

**Figure 4: Board handling**

Proper handling of the CM6 is critical to ensure proper operation and long-term reliability. When unpacking the board, and whenever handling it thereafter, be sure to hold the board by the front panel or the card ejectors as shown in the drawing on the left. Do not hold the board by the circuit card edges, the heat sink, or the connectors.

#### **Initial Inspection**

After unpacking the CM6, you should inspect it for visible damage that could have occurred during shipping or unpacking. If damage is observed (usually in the form of bent component leads or loose socketed components), contact GE Intelligent Platforms for additional instructions. Depending on the severity of the damage, it may need to be returned to the factory for repair. **DO NOT apply power to the board if it has visible damage.** Doing so may cause further, possibly irreparable damage, as well as introduce a fire or shock hazard.

## **Attention:**

Do not insert a CM6 board in a 3/6U 64-bit Backplane because this may damage electrical interfaces at the CM6.

Please take care that the CM6 is configured for use as a CompactPCI controller in delivery state (CPCI bridge in transparent mode).

For use as a peripheral board (CPCI bridge in NONtransparent mode) please insert the CM6 into a CPCI system slot, power it on and reconfigure the CPCI bridge with the U-Boot command 'bridge':

bridge cpci program default peripheral.

#### **Delivery Volume**

Please check that the delivered package contains the following items:

| Table 1: Delivery volume |       |                                                                                                    |

|--------------------------|-------|----------------------------------------------------------------------------------------------------|

| Qty.                     | Item  | Purpose                                                                                            |

| 1                        | CM6   | CompactPCI Single Board Computer                                                                   |

| 1                        | CDROM | Technical Product Information<br>with driver software and manuals in Adobe Acrobat<br>(PDF) format |

The manual files are also available through the World Wide Web from our web server:

http://www.ge-ip.com

## **Available Accessories**

The following table lists accessory options which are available for the CM6:

|       | Table 2: Accessory options for CM6 |  |

|-------|------------------------------------|--|

| Item  | Purpose                            |  |

| CTM19 | Transition module, 3U x 4HP        |  |

Please contact the sales department or your sales representative for latest information on options and accessories.

Accessories are subject to change without notice.

## CHAPTER 3 Installation

| Chapter Scope  | This chapter covers the installation of the CM6 CompactPCI Single Board<br>Computer in a CompactPCI backplane and initial power-on operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General advice | Please observe all safety procedures to avoid damaging system and protect operators and users.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                | <ul> <li>Unpacking and Handling</li> <li>Please read the manual carefully before unpacking the module or fitting the device into your system. Also adhere to the following:</li> <li>Observe all precautions for electrostatic sensitive modules</li> <li>If the product contains batteries, please do not place the board on conductive surfaces, anti-static plastic, or sponge, which can cause shots and lead to battery or board trace damage.</li> <li>Please do not exceed the specified operational temperatures. Note that batteries and storage devices might also have temperature restrictions.</li> <li>Keep all original packaging material for future storage or warranty shipments of the board.</li> </ul> |  |  |

|                | <b>ESD</b><br>Electrostatic Discharge (ESD) is a major cause of electronic component failure.<br>The CM6 has been packed in a static-safe bag which protects the board from<br>ESD while the board is in the bag. From the time the board is removed from the<br>anti static bag until it is properly mounted in a backplane, extreme care should                                                                                                                                                                                                                                                                                                                                                                           |  |  |

be taken to avoid damaging board through electrostatic discharges. See page 25

for details on how to prevent 'zapping' the board with ESD.

#### **General Advisories**

Before installing or removing any board, please ensure that the system power and external supplies have been turned off.

Check that jumpers and piggybacks are correctly configured for your application. Mount the board, piggyback, or transition module very carefully. See also sections on additional advisories below.

Do not restore power until you are sure that all modules are fitted correctly and all connections have been made properly.

#### Advisories for CompactPCI products

Mount the CPU board carefully in the CPCI bus slot. Note that on some boards connectors are used for I/O purposes which must not be inserted into a CPCI bus backplane. A transition module must be used instead.

#### Minimum System Requirements

As shipped, the CM6 has been thoroughly tested, and is nearly ready for use in your system. In order to verify CM6 operation for the first time, it is suggested that you only configure a minimal system

Because the CM6 is available in several options the description in this chapter is related to the standard configuration.

The following items are required to start the CM6 in a standard configuration:

#### Backplane and Power Supply

You will need a standard 3U 32bit CompactPCI backplane wired into a regulated power supply capable of providing stable low noise +5 V and +3.3 V sources. Make sure that the supply is capable of meeting the total power requirements of the CM6. Please refer to chapter "Specifications" on page 65 for details.

Initially, you have to plug the CM6 into your 3U system slot of your CPCI system. Please make sure that you do not have the power supply turned ON when the CM6 is plugged into your backplane.

The CTM19 is a 3U x 80 mm rear I/O module which has to be plugged into the CM6 with the backplane between.

#### Installation

### **Attention:**

## Do not insert a CM6 board in a 3/6U 64-bit Backplane because this may damage electrical interfaces at the CM6.

After making sure that you have installed the CM6 properly into your CPCI backplane, connect a VT102 terminal at COM1 (use CTM19) and set the terminal to 115200 baud rate, 8-bit, non-parity. When the board is completely reset the status LED at the board is off and will be set to green by the boot loader at start.

When the processor should begin executing initial boot loader resident routines and when the boot loader is complete the board status LED at the transition module is switched off.

Figure 5: Board in card cage

Please see chapter "Interfaces" for details on onboard interfaces. The location of the CM6 interfaces is shown on page 33.

## Initial Power-On Operation

After a few seconds, the CM6 system boot message will appear on the terminal and the status LED is set to green.

If you have seen all the messages so far, you can be confident that the board is running properly and is ready to be installed and setup for your application.

## CHAPTER 4 Interfaces

#### **Chapter Scope**

This chapter describes the interfaces of the CM6 CompactPCI Single Board Computer located on the board and on the front panel. Each section on a particular interface includes a graphics illustration of the connector and a pin assignment table as well as notes on certain signal line characteristics, if necessary.

For interfaces of the transition module, please refer to the appropriate chapters found in the "Appendices" to this manual.

Figure 6: Board photo

## **Front Panel Interfaces**

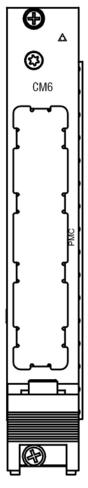

Refer to figure 7 for front panel of the CM6 board.

Figure 7: CM6 front panel

## **CM6 Connectors**

This chapter describes connector pin assignments on the CM6. A pin assignment description for available transition module can be found in the corresponding appendix chapters.

### **CPCI** connector reference

The CPCI specification numbers the CPCI connectors from bottom to top J1, J2. The CPCI connectors on the CM6 are J7001and J7001 respectively.

Table 3: CM6 connectors

| Signal groups                | Pin description                |

|------------------------------|--------------------------------|

| COM1, COM2 signals           | C1, C2                         |

| General Purpose I/O          | GPIO                           |

| PMC I/O signals              | PMCIO                          |

| External Reset Input         | PRST#                          |

| COP Debug Interface          | COP                            |

| LAN Port A and LAN Port B    | LPA; LPB                       |

| Signals separated by a slash | Alternative signal assignments |

| NC                           | not connected                  |

## **Attention:**

Do not insert a CM6 board in a 3/6U 64-bit Backplane because this may damage electrical interfaces at the CM6.

## CompactPCI bus Connector J7001 and J7002

This interface is used for connection to a standard CPCI backplane.

| J7002    | А                 | В                   | С                            | D           | Е                   | F          |

|----------|-------------------|---------------------|------------------------------|-------------|---------------------|------------|

| 22       | GA4               | GA3                 | GA2                          | GA1         | GA0                 | GND        |

| 21       | CLK6              | GND                 | COP_TDI                      | SW CFG#     | HW WP#              | GND        |

| 20       | CLK5              | GND                 | COP_TMS                      | COP_TRST#   | COP_TCK             | GND        |

| 19       | GND               | GND                 | CKSTPIN#                     | CKSTPOUT    | BFAIL#              | GND        |

| 18       | PMCIO03/GPIO2     | PMCIO02/GPIO1       | PMCIO01/GPIO0                | COP TDO     | COP SRST#           | GND        |

| 17       | PMCIO05/GPIO4     | PMCIO04/GPIO3       | PRST#                        | REQ6#       | GNT6#               | GND        |

| 16       | PMCIO07/GPIO6     | PMCIO06/GPIO5       | DEG#                         | GND         | COP_HRST#           | GND        |

| 15       | PMCIO09/FKILL#    | PMCIO08/GPIO7       | FAL#                         | REQ5#       | GNT5#               | GND        |

| 14       | PMCIO12           | PMCIO11             | PMCIO10                      | C1_RXD      | C1_RTS              | GND        |

| 13       | PMCIO15           | PMCIO14             | PMCIO13                      | C1_TXD      | C2_RTS+             | GND        |

| 12       | PMCIO18           | PMCIO17             | PMCIO16                      | C1_CTS      | C2_RTS-             | GND        |

| 11       | PMCIO21           | PMCIO20             | PMCIO19                      | LPB_DA+     | LPB_DB+             | GND        |

| 10       | PMCIO24           | PMCIO23             | PMCIO22                      | LPB_DA-     | LPB_DB-             | GND        |

| 9        | PMCIO26/52        | PMCIO25             | C2_CTS+                      | LPB_DC+     | LPB_DD+             | GND        |

| 8        | PMCIO28           | PMCIO27             | C2_CTS-                      | LPB_DC-     | LPB_DD-             | GND        |

| 7        | PMCIO30/37        | PMCIO29             | C2_TXD+                      | LPA_DB+     | LPA_DA+             | GND        |

| 6        | PMCIO32/39        | PMCIO31             | C2_TXD-                      | LPA_DB-     | LPA_DA-             | GND        |

| 5        | PMCIO38/44        | PMCIO36/42          | C2_RXD+                      | LPA_DD+     | LPA_DC+             | GND        |

| 4        | VIO <sup>b</sup>  | PMCIO50             | C2_RXD-                      | LPA_DD-     | LPA_DC-             | GND        |

| 3        | CLK4              | GND                 | GNT3#                        | REQ4#       | GNT4#               | GND        |

| 2        | CLK2              | CLK3                | SYSEN#                       | GNT2#       | REQ3#               | GND        |

| 1        | CLK1              | GND                 | REQ1#                        | GNT1#       | REQ2#               | GND        |

| J7001    | A                 | B                   | C                            | D           | E                   | F          |

| 25       | +5 V              | REQ64# <sup>a</sup> | ENUM#                        | +3.3 V      | +5 V                | GND        |

| 24       | AD01              | +5 V                | VIO <sup>b</sup>             | AD00        | ACK64# <sup>a</sup> | GND        |

| 23       | +3.3 V            | AD04                | AD03                         | +5 V        | AD02                | GND        |

| 22<br>21 | AD07              | GND                 | +3.3 V                       | AD06        | AD05                | GND        |

|          | +3.3 V            | AD09<br>GND         | AD08<br>VIO <sup>b</sup>     | M66EN       | C/BE0#              | GND<br>GND |

| 20<br>19 | AD12<br>+3.3 V    | AD15                | AD14                         | AD11<br>GND | AD10<br>AD13        | GND<br>GND |

| 19       | +5.5 V<br>SERR#   | GND                 | +3.3 V                       | PAR         | C/BE1#              | GND        |

| 18       | +3.3 V            | reserved            |                              | GND         | PERR#               | GND        |

| 17       | +3.3 V<br>DEVSEL# | GND                 | reserved<br>VIO <sup>b</sup> | STOP#       | LOCK#               | GND<br>GND |

| 15       | +3.3 V            | FRAME#              | IRDY#                        | BDSEL#      | TRDY#               | GND        |

| 13       | +5.5 V<br>KEY     | KEY                 | KEY                          | KEY         | KEY                 | KEY        |

| 12-14    | AD18              | AD17                | AD16                         | GND         | C/BE2#              | GND        |

| 10       | AD18<br>AD21      | GND                 | +3.3 V                       | AD20        | AD19                | GND        |

| 9        | C/BE3#            | IDSEL               | AD23                         | GND         | AD19<br>AD22        | GND        |

| 8        | AD26              | GND                 | VIO <sup>b</sup>             | AD25        | AD22<br>AD24        | GND        |

| 8<br>7   | AD20<br>AD30      | AD29                | AD28                         | GND         | AD24<br>AD27        | GND        |

| 6        | REQ0#             | PCIPRESENT#         | +3.3 V                       | CLK0        | AD27<br>AD31        | GND        |

| 5        | reserved          | reserved            | RST#                         | GND         | GNT0#               | GND        |

| 4        | reserved          | GND                 | VIO <sup>b</sup>             | reserved    | reserved            | GND        |

| 3        | INTA#             | INTB#               | INTC#                        | +5 V        | INTD#               | GND        |

| 2        | TCK               | +5 V                | TMS                          | TDO         | TDI                 | GND        |

| 1        | +5 V              | -12V                | TRST#                        | +12V        | +5 V                | GND        |

| 1        | · J · V           | 1∠ ¥                | 11017                        | · 12 V      |                     | 0.00       |

<sup>a</sup> These signals are not used on the CM6, but have a pull-up to VIO <sup>b</sup> The VIO signals are either 5 V or 3.3 V, depending on backplane Reserved – Pin is reserved in the PICMG 2.0 specification. It is not used on the CM6 board

## PMC Connectors J7101, J7102, J7103 and J7104

The following table lists the pin assignments of the onboard PMC connector. The PMC slot is PCI 64 bit and 66 MHz capable and works with the internal PCI-PCIe bridge Pericom Pi7C9X130. The PMC is electrical and mechanical compliant to the specification IEEE 1386 and 1386.1 with enhancements of the Processor PMC Standard VITA 32-2003. The enhancements provide pins for a second device (IDSELB and REQB#/GNTB#) and support non-monarch processor PMC cards.

The PCI signaling voltage V(I/O) at the PMC is fixed to 3.3 V but the CM6 PMC is tolerant to 5 V signaling, too.

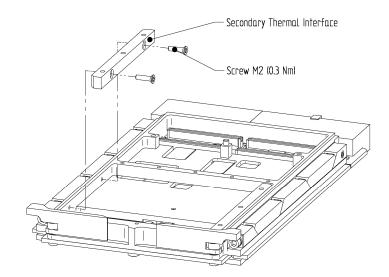

## Secondary Thermal Interface

On conduction-cooled versions of boards and mezzanines the PMC modules may be equipped with optional Secondary Thermal Interfaces. If the PMCs do not fit into their sockets on the CM6 base board then you can remove them. Use a matching TORX screw driver to remove the Secodary Thermal Interfaces. For mounting use a torque of 0.3 Nm to fix the screws or use minimum force to tighten the screws. Add only a short turn ( $\sim$ 1/16th) when the screw starts to get tight.

Figure 8: Mounting of Secondary Thermal Interface on PMC module

|          |                  |          | _   |     | <b>I</b> |                  |          |

|----------|------------------|----------|-----|-----|----------|------------------|----------|

| P7101    | P7102            | P7103    | Pin | Pin | P7101    | P7102            | P7103    |

| TCK      | +12 V            | Reserved | 01  | 02  | -12 V    | TRST#            | GND      |

| GND      | TMS              | GND      | 03  | 04  | INTA#    | TDO              | C/BE7    |

| INTB#    | TDI              | C/BE6    | 05  | 06  | INTB#    | GND              | C/BE5    |

| PRESENT# | GND              | C/BE4    | 07  | 08  | +5 V     | Reserved         | GND      |

| INTD#    | Reserved         | V(I/O)   | 09  | 10  | Reserved | Reserved         | PAR64    |

| GND      | PUP <sup>a</sup> | AD63     | 11  | 12  | NC       | +3.3 V           | AD62     |

| PCICLK   | PCIRST#          | AD61     | 13  | 14  | GND      | PDN <sup>a</sup> | GND      |

| GND      | +3.3 V           | GND      | 15  | 16  | GNT0#    | PDN <sup>a</sup> | AD60     |

| REQ0#    | PME#             | AD59     | 17  | 18  | +5 V     | GND              | AD58     |

| V(I/O)   | AD30             | AD57     | 19  | 20  | AD31     | AD29             | GND      |

| AD28     | GND              | V(I/O)   | 21  | 22  | AD27     | AD26             | AD56     |

| AD25     | AD24             | AD55     | 23  | 24  | GND      | +3.3 V           | AD54     |

| GND      | AD20             | AD53     | 25  | 26  | C/BE3#   | AD23             | GND      |

|          | (IDSEL)          |          |     |     |          |                  |          |

| AD22     | +3.3 V           | GND      | 27  | 28  | AD21     | AD20             | AD52     |

| AD19     | AD18             | AD51     | 29  | 30  | +5 V     | GND              | AD50     |

| V(I/O)   | AD16             | AD49     | 31  | 32  | AD17     | C/BE2#           | GND      |

| FRAME#   | GND              | GND      | 33  | 34  | GND      | AD19             | AD48     |

|          |                  |          |     |     |          | (IDSELB)         |          |

| GND      | TRDY#            | AD47     | 35  | 36  | IRDY#    | +3.3 V           | AD46     |

| DEVSEL#  | GND              | AD45     | 37  | 38  | +5 V     | STOP#            | GND      |

| PCIXCAP  | PERR#            | V(I/O)   | 39  | 40  | LOCK#    | GND              | AD44     |

| Reserved | +3.3 V           | AD43     | 41  | 42  | RES.     | SERR#            | AD42     |

| PAR      | C/BE1#           | AD41     | 43  | 44  | GND      | GND              | GND      |

| V(I/O)   | AD14             | GND      | 45  | 46  | AD15     | AD13             | AD40     |

| AD12     | M66EN            | AD39     | 47  | 48  | AD11     | AD10             | AD38     |

| AD9      | AD8              | AD37     | 49  | 50  | +5 V     | +3.3 V           | GND      |

| GND      | AD7              | GND      | 51  | 52  | C/BE0#   | REQB#            | AD36     |

| AD6      | +3.3 V           | AD35     | 53  | 54  | AD5      | GNTB#            | AD34     |

| AD4      | Reserved         | AD33     | 55  | 56  | GND      | GND              | GND      |

| V(I/O)   | EREADY           | V(I/O)   | 57  | 58  | AD3      | NC               | AD32     |

| AD2      | GND              | Reserved | 59  | 60  | AD1      | RSTOUT#          | Reserved |

| AD0      | ACK64#           | Reserved | 61  | 62  | +5 V     | +3.3 V           | GND      |

| GND      | GND              | GND      | 63  | 64  | REQ64#   | NC               | Reserved |

|          |                  |          |     |     |          |                  |          |

Table 5: PMC connector pin assignments

$^a$  Weak 10k $\Omega$  pull-down (PDN) to GND and pull-up (PUP) to VIO.

|    | NC          | Not connected                                      |

|----|-------------|----------------------------------------------------|

| ~Ø | Reserved    | Reserved. Do not connect anything                  |

|    | V(I/O)      | I/O Voltage, connected with +3.3 V                 |

|    | -12 V/+ 12V | Only available if connected at the CPCI backplane. |

Due to the limited rear I/O pins not all 64 PMCIO signals are routed.

| Pin | P710     | 4 (Pn4)           | Pin |

|-----|----------|-------------------|-----|

| 01  | PMCIO01* | PMCIO02*          | 02  |

| 03  | PMCIO03* | PMCIO04*          | 04  |

| 05  | PMCIO05* | PMCIO06*          | 06  |

| 07  | PMCIO07* | PMCIO08*          | 08  |

| 09  | PMCIO09* | PMCIO10           | 10  |

| 11  | PMCIO11  | PMCIO12           | 12  |

| 13  | PMCIO13  | PMCIO14           | 14  |

| 15  | PMCIO15  | PMCIO16           | 16  |

| 17  | PMCIO17  | PMCIO18           | 18  |

| 19  | PMCIO19  | PMCIO20           | 20  |

| 21  | PMCIO21  | PMCIO22           | 22  |

| 23  | PMCIO23  | PMCIO24           | 24  |

| 25  | PMCIO25  | PMCIO26*          | 26  |

| 27  | PMCIO27  | PMCIO28           | 28  |

| 29  | PMCIO29  | PMCIO30*          | 30  |

| 31  | -        | PMCIO32*          | 32  |

| 33  | -        | -                 | 34  |

| 35  | -        | PMCIO36*          | 36  |

| 37  | PMCIO37* | PMCIO38*          | 38  |

| 39  | PMCIO39* | -                 | 40  |

| 41  | -        | PMCIO42*          | 42  |

| 43  | -        | PMCIO44*          | 44  |

| 45  | -        | -                 | 46  |

| 47  | -        | -                 | 48  |

| 49  | -        | PMCIO50           | 50  |

| 51  | -        | PMCIO52*          | 52  |

| 53  | -        | -                 | 54  |

| 55  | -        | -                 | 56  |

| 57  | -        | -                 | 58  |

| 59  | -        | -                 | 60  |

| 61  | -        | -                 | 62  |

| 63  | -        | -                 | 64  |

| (B) |          | ls are not in eac |     |

Table 6: P7104 connector pin assignments

\* These signals are not in each configuration available at rear cPCI\_J2 connector see section below for details.

## PMCIO – cPCI\_J2 Configuration

Not all possible 64 PMCIO are connected to the rear cPCI\_J2 connector. Additional to this restriction some PMCIOs signals are alternative assigned with other PMCIOs or signals. See below the signals which are connected from the PMC connector J4 (P7104) to the cPCI\_J2 connector.

Either PMCIO01...08 or GPIO 0...7 are connected to the rear and with FlashKill option PMCIO09 is replaced with flash kill signal (FKILL#).

the table below shows the standard PMCIO – cPCI J2 configuration:

| Pin | P71       | Pin      |    |

|-----|-----------|----------|----|

| 01  | PMCIO01*  | PMCIO02* | 02 |

| 03  | PMCIO03*  | PMCIO04* | 04 |

| 05  | PMCIO05*  | PMCIO06* | 06 |

| 07  | PMCIO07*  | PMCIO08* | 08 |

| 09  | PMCIO09** | PMCIO10  | 10 |

| 11  | PMCIO11   | PMCIO12  | 12 |

| 13  | PMCIO13   | PMCIO14  | 14 |

| 15  | PMCIO15   | PMCIO16  | 16 |

| 17  | PMCIO17   | PMCIO18  | 18 |

| 19  | PMCIO19   | PMCIO20  | 20 |

| 21  | PMCIO21   | PMCIO22  | 22 |

| 23  | PMCIO23   | PMCIO24  | 24 |

| 25  | PMCIO25   | -        | 26 |

| 27  | PMCIO27   | PMCIO28  | 28 |

| 29  | PMCIO29   | PMCIO30  | 30 |

| 31  | PMCIO31   | PMCIO32  | 32 |

| 33  | -         | -        | 34 |

| 35  | -         | PMCIO36  | 36 |

| 37  | -         | PMCIO38  | 38 |

| 39  | -         | -        | 40 |

| 41  | -         | -        | 42 |

| 43  | -         | -        | 44 |

| 45  | -         | -        | 46 |

| 47  | -         | -        | 48 |

| 49  | -         | PMCIO50  | 50 |

| 51  | -         | PMCIO52  | 52 |

| 53  | -         | -        | 54 |

| 55  | -         | -        | 56 |

| 57  | -         | -        | 58 |

| 59  | -         | -        | 60 |

| 61  | -         | -        | 62 |

| 63  | -         | -        | 64 |

Table 7: P7104/P7002 connectors pin assignments

| J7002 | А                | В        | С        | D         | E         | F   |

|-------|------------------|----------|----------|-----------|-----------|-----|

| 22    | GA4              | GA3      | GA2      | GA1       | GA0       | GND |

| 21    | CLK6             | GND      | COP_TDI  | SW_CFG#   | HW_WP#    | GND |

| 20    | CLK5             | GND      | COP_TMS  | COP_TRST# | COP_TCK   | GND |

| 19    | GND              | GND      | CKSTPIN# | CKSTPOUT  | BFAIL#    | GND |

| 18    | PMCIO03*         | PMCIO02* | PMCIO01* | COP_TDO   | COP_SRST# | GND |

| 17    | PMCIO05*         | PMCIO04* | PRST#    | REQ6#     | GNT6#     | GND |

| 16    | PMCIO06*         | PMCIO06* | DEG#     | GND       | COP_HRST# | GND |

| 15    | PMCIO09**        | PMCIO08* | FAL#     | REQ5#     | GNT5#     | GND |

| 14    | PMCIO12          | PMCIO11  | PMCIO10  | C1_RXD    | C1_RTS    | GND |

| 13    | PMCIO15          | PMCIO14  | PMCIO13  | C1_TXD    | C2_RTS+   | GND |

| 12    | PMCIO18          | PMCIO17  | PMCIO16  | C1_CTS    | C2_RTS-   | GND |

| 11    | PMCIO21          | PMCIO20  | PMCIO19  | LPB_DA+   | LPB_DB+   | GND |

| 10    | PMCIO24          | PMCIO23  | PMCIO22  | LPB_DA-   | LPB_DB-   | GND |

| 9     | PMCIO52          | PMCIO25  | C2_CTS+  | LPB_DC+   | LPB_DD+   | GND |

| 8     | PMCIO28          | PMCIO27  | C2_CTS-  | LPB_DC-   | LPB_DD-   | GND |

| 7     | PMCIO30          | PMCIO29  | C2_TXD+  | LPA_DB+   | LPA_DA+   | GND |

| 6     | PMCIO32          | PMCIO31  | C2_TXD-  | LPA_DB-   | LPA_DA-   | GND |

| 5     | PMCIO38          | PMCIO36  | C2_RXD+  | LPA_DD+   | LPA_DC+   | GND |

| 4     | VIO <sup>b</sup> | PMCIO50  | C2_RXD-  | LPA_DD-   | LPA_DC-   | GND |

| 3     | CLK4             | GND      | GNT3#    | REQ4#     | GNT4#     | GND |

| 2     | CLK2             | CLK3     | SYSEN#   | GNT2#     | REQ3#     | GND |

| 1     | CLK1             | GND      | REQ1#    | GNT1#     | REQ2#     | GND |

## Note

\*PMCIO01...08 will be replaced with GPIO 0...7 at option with available GPIOs

Note

\*\*PMCIO09 will be replaced with flash kill signal (FKILL#) option.

## **PMCIO Configuration:**

There is an option available which is optimized for the G2 Graphic PMC card from GE Intelligent Platforms.

| Pin | P7        | 104 (Pn4) | Pin |

|-----|-----------|-----------|-----|

| 01  | PMCIO01*  | PMCIO02*  | 02  |

| 03  | PMCIO03*  | PMCIO04*  | 04  |

| 05  | PMCIO05*  | PMCIO06*  | 06  |

| 07  | PMCIO07*  | PMCIO08*  | 08  |

| 09  | PMCIO09** | PMCIO10   | 10  |

| 11  | PMCIO11   | PMCIO12   | 12  |

| 13  | PMCIO13   | PMCIO14   | 14  |

| 15  | PMCIO15   | PMCIO16   | 16  |

| 17  | PMCIO17   | PMCIO18   | 18  |

| 19  | PMCIO19   | PMCIO20   | 20  |

| 21  | PMCIO21   | PMCIO22   | 22  |

| 23  | PMCIO23   | PMCIO24   | 24  |

| 25  | PMCIO25   | PMCIO26   | 26  |

| 27  | PMCIO27   | PMCIO28   | 28  |

| 29  | PMCIO29   | -         | 30  |

| 31  | PMCIO31   | -         | 32  |

| 33  | -         | -         | 34  |

| 35  | -         | -         | 36  |

| 37  | PMCIO37   | -         | 38  |

| 39  | PMCIO39   | -         | 40  |

| 41  | -         | PMCIO42   | 42  |

| 43  | -         | PMCIO44   | 44  |

| 45  | -         | -         | 46  |

| 47  | -         | -         | 48  |

| 49  | -         | PMCIO50   | 50  |

| 51  | -         | -         | 52  |

| 53  | -         | -         | 54  |

| 55  | -         | -         | 56  |

| 57  | -         | -         | 58  |

| 59  | -         | -         | 60  |

| 61  | -         | -         | 62  |

| 63  | -         | -         | 64  |

Table 8: P7104/P7002 connectors pin assignments

| J7002 | А                | В        | С        | D         | Е         | F   |

|-------|------------------|----------|----------|-----------|-----------|-----|

| 22    | GA4              | GA3      | GA2      | GA1       | GA0       | GND |

| 21    | CLK6             | GND      | COP_TDI  | SW_CFG#   | HW_WP#    | GND |

| 20    | CLK5             | GND      | COP_TMS  | COP_TRST# | COP_TCK   | GND |

| 19    | GND              | GND      | CKSTPIN# | CKSTPOUT  | BFAIL#    | GND |

| 18    | PMCIO03*         | PMCIO02* | PMCIO01* | COP_TDO   | COP_SRST# | GND |

| 17    | PMCIO05*         | PMCIO04* | PRST#    | REQ6#     | GNT6#     | GND |

| 16    | PMCIO06*         | PMCIO06* | DEG#     | GND       | COP_HRST# | GND |

| 15    | PMCIO09**        | PMCIO08* | FAL#     | REQ5#     | GNT5#     | GND |

| 14    | PMCIO12          | PMCI011  | PMCIO10  | C1_RXD    | C1_RTS    | GND |

| 13    | PMCIO15          | PMCIO14  | PMCIO13  | C1_TXD    | C2_RTS+   | GND |

| 12    | PMCIO18          | PMCIO17  | PMCIO16  | C1_CTS    | C2_RTS-   | GND |

| 11    | PMCIO21          | PMCIO20  | PMCIO19  | LPB_DA+   | LPB_DB+   | GND |

| 10    | PMCIO24          | PMCIO23  | PMCIO22  | LPB_DA-   | LPB_DB-   | GND |

| 9     | PMCIO26          | PMCIO25  | C2_CTS+  | LPB_DC+   | LPB_DD+   | GND |

| 8     | PMCIO28          | PMCIO27  | C2_CTS-  | LPB_DC-   | LPB_DD-   | GND |

| 7     | PMCIO37          | PMCIO29  | C2_TXD+  | LPA_DB+   | LPA_DA+   | GND |

| 6     | PMCIO39          | PMCIO31  | C2_TXD-  | LPA_DB-   | LPA_DA-   | GND |

| 5     | PMCIO44          | PMCIO42  | C2_RXD+  | LPA_DD+   | LPA_DC+   | GND |

| 4     | VIO <sup>b</sup> | PMCIO50  | C2_RXD-  | LPA_DD-   | LPA_DC-   | GND |

| 3     | CLK4             | GND      | GNT3#    | REQ4#     | GNT4#     | GND |

| 2     | CLK2             | CLK3     | SYSEN#   | GNT2#     | REQ3#     | GND |

| 1     | CLK1             | GND      | REQ1#    | GNT1#     | REQ2#     | GND |

|       |                  |          |          |           |           |     |

Note

\*PMCIO01...08 will replaced with optional GPIO 0...7

Note

\*\*PMCIO09 will replaced with flash kill option (FKILL#)

# **Transition Module**

Please refer to the appendix chapters for interface location and connector pinouts for the optional transition module CTM19 (Appendix A).

# CHAPTER 5 Resources

| Chapter Scope        | This chapter describes system resources, such as memory mapping, register set<br>and default interrupt request assignments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Map          | The MPC8641 supports a flexible 36-bit physical address map. Conceptually, the address map consists of local space and external address space. The local address map spans 64 GByte. The e600 core uses a 52-bit interim virtual address to address 4 PBytes of virtual memory, and a 36-bit physical address to address 64 GByte of physical memory. The MPC8641 can be made part of an even larger system address space through the mapping of translation windows. This functionality is included in the address translation and mapping units (ATMUs). Both inbound and outbound translation windows are provided. The ATMUs allow the MPC8641 to be part of the larger address maps such as the PCI Express 64-bit address environment. |

| Local Bus Controller | The local bus controller (LBC) of the MPC8641 in the CM6 is used as a general-purpose machine which supports compatible SRAM, ROM and peripherals with 8-, 16-, 32-bit devices. The supplied chip selects of the LBC are connected to a 32-bit wide boot and application Flash ROM, an 8-bit wide nvSRAM/RTC device and an 8-bit CPLD with CM6 unique status and control registers.<br>After reset the boot code is fetched from the boot/application Flash ROM. The address map is defined by the boot loader respective depends on the operating system please refer to the appropriate software manual.                                                                                                                                   |

# **CPLD Registers**

One device connected at the LBC is the CPLD (U1949) which provides seven CM6 specific control and status registers. The CPLD register are connected to the Local Bus Controller at chip select LCS1 with 8-bit data width. The bit description is in little endian, least significant bit is at the right and most significant bit at the left end of the byte.

Reset Source Register (RSR) Address: Base + Offset 0 Size: 8 bit

| Bit | Name      | Write            | Read                        | Default   |

|-----|-----------|------------------|-----------------------------|-----------|

| 0   | R_PWR     | any write clears | 1: last reset caused by     | not       |

|     |           | the bit *        | voltage monitor             | defined   |

| 1   | R_THERM   | any write clears | 1: last reset caused by     | not       |

|     |           | the bit *        | power down of the thermal   | defined   |

|     | D DCI     | · · · ·          | protection                  |           |

| 2   | R_PCI     | any write clears | 1: 1ast reset caused by     | not       |

|     |           | the bit *        | Reset button, cPCI Reset    | defined   |

|     |           |                  | (non System only) or        |           |

|     |           |                  | RESETOUT# from PMC          |           |

| 3   | reserved  | -                | 0                           | n/a       |

| 4   | R_HRSTREQ | any write clears | 1: last reset caused by CPU | not       |

|     |           | the bit *        | reset request               | defined   |

|     |           |                  | Must be cleared before a    |           |

|     |           |                  | CPU reset request is        |           |

|     |           |                  | performed                   |           |

| 5   | R_COPRST  | any write clears | 1: last reset caused by COP | not       |

|     |           | the bit *        | Interface HRESET or         | defined   |

|     |           |                  | SRESET                      |           |